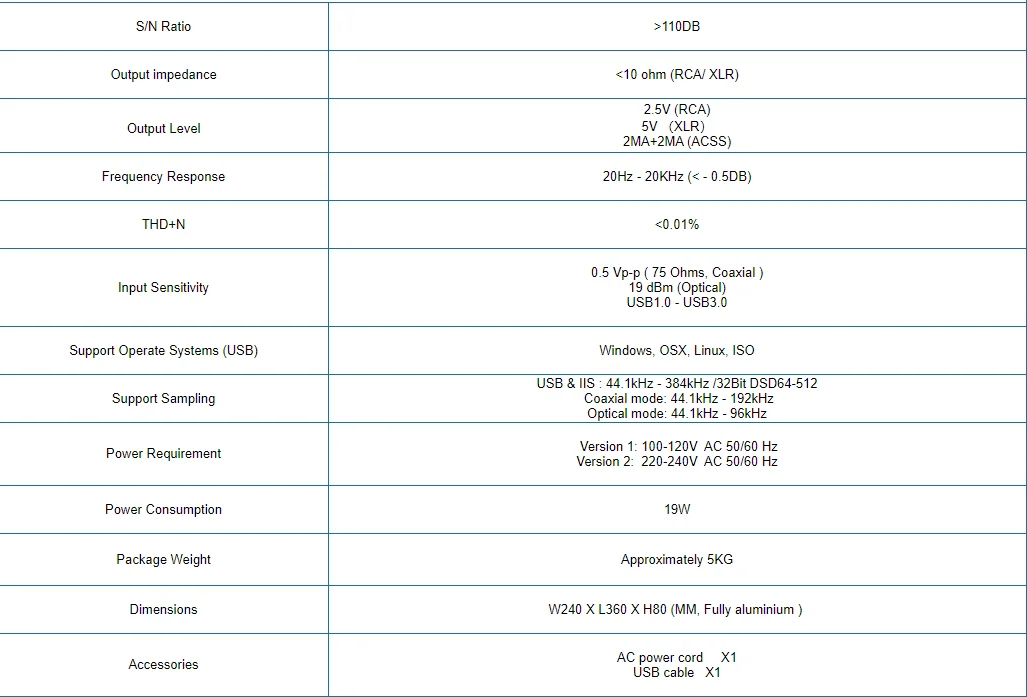

R-1 (version 2021)

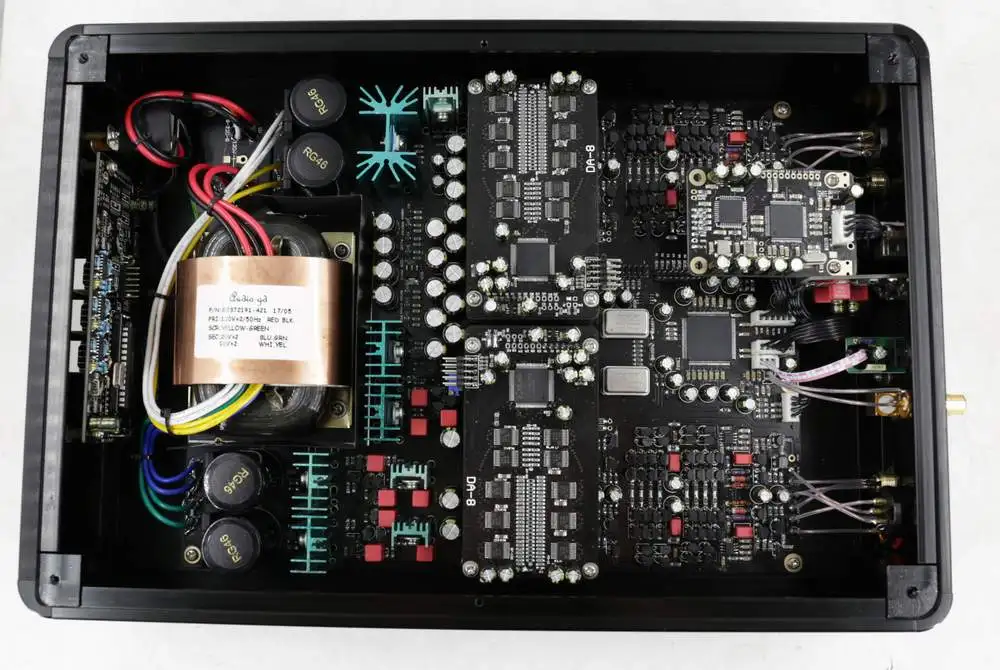

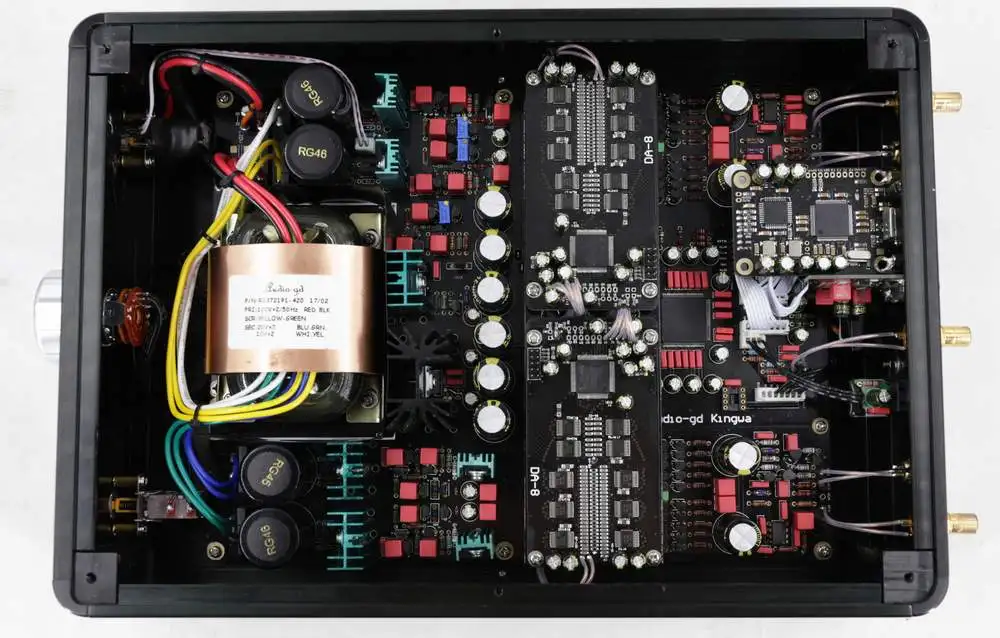

Fully discrete, truly balanced current transfer design.

Four sets of separate DSD hardware decoder.

Eight sets of R-2R Da modules make up of two channel balanced push-pull decoder.

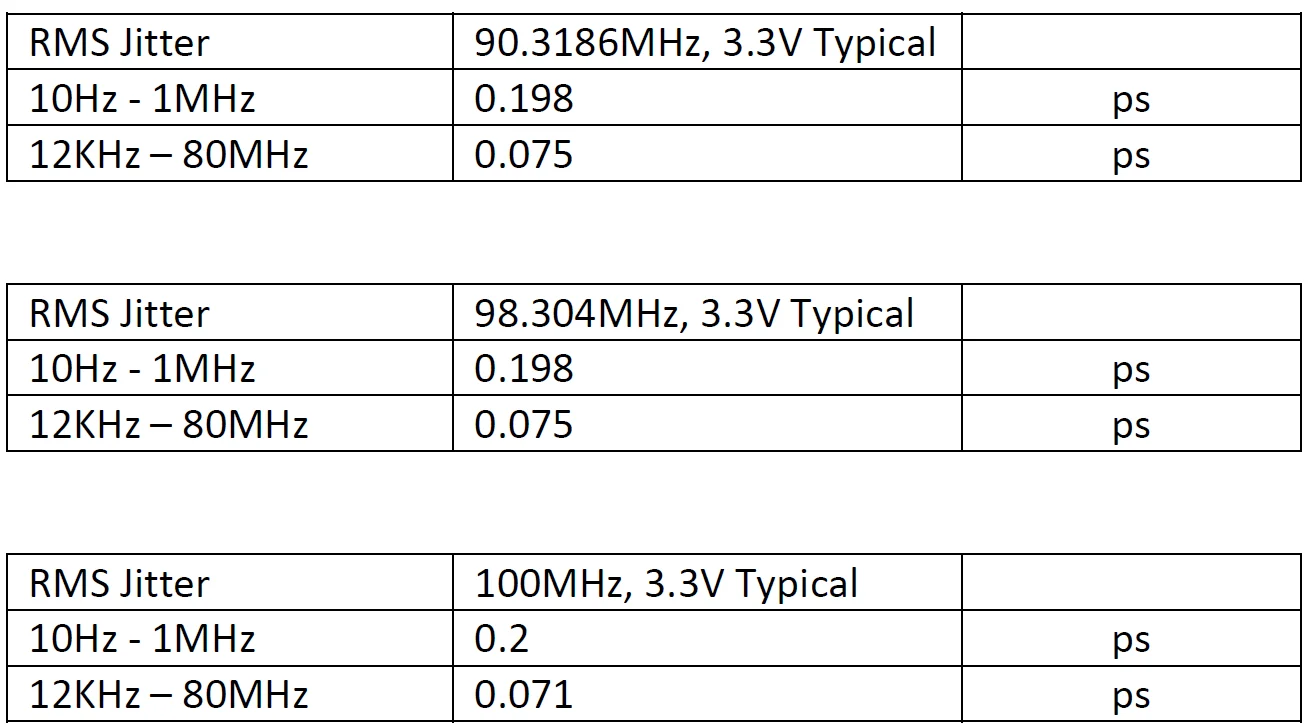

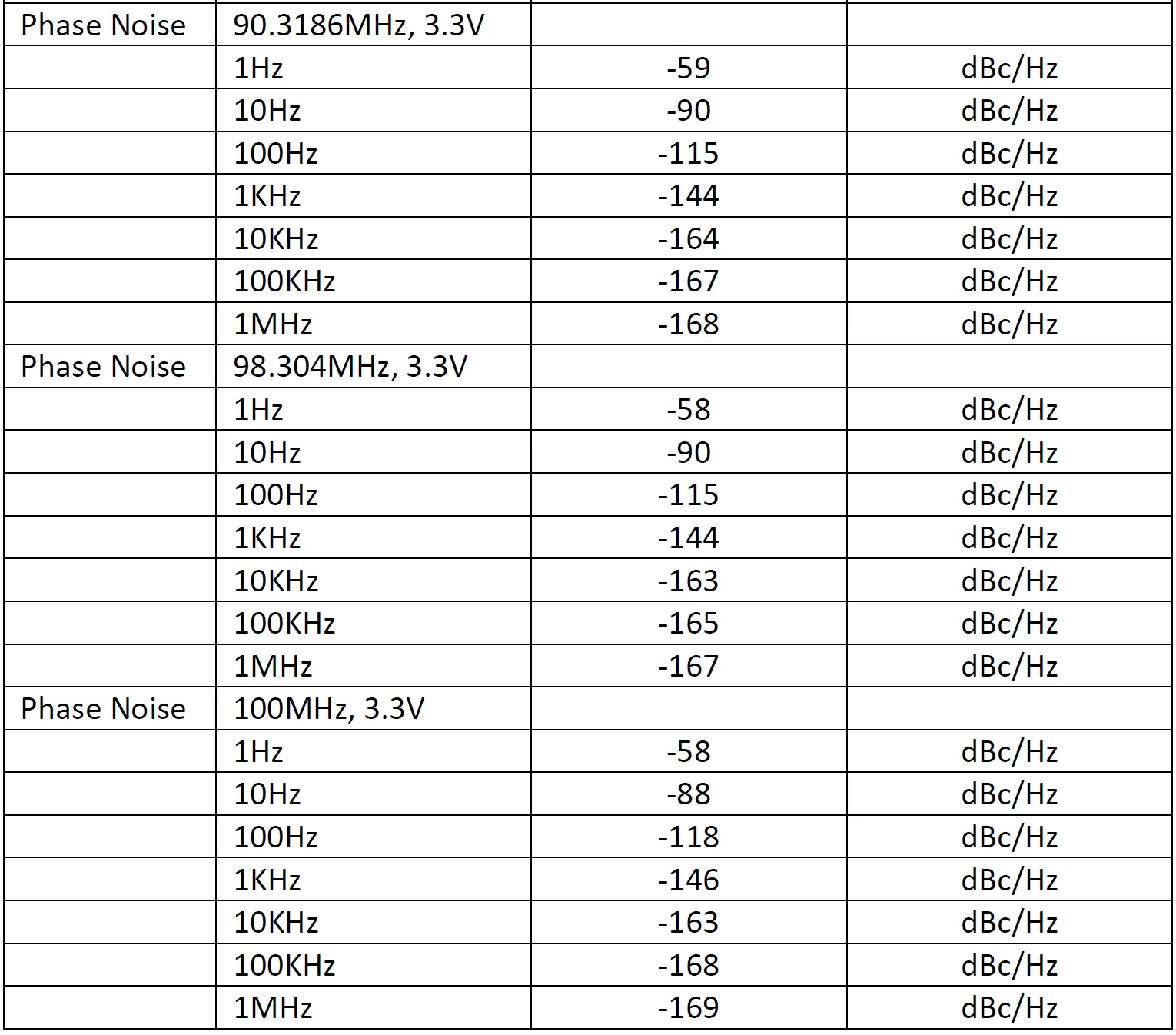

Two accusilicon clocks with frequency up to 90 / 98mhz provide the synchronous clock of the whole machine without PLL upregulation.

32bit / 384k asynchronous transmission amanero USB interface, using FPGA synchronous clock.

USB / HDMI supports DXD and DSD.

The whole digital circuit is composed of one FPGA and five CPLD programmable devices, which separate different functional circuits to isolate interference,

The parallel data processing mode with the fastest transmission speed is applied, and firmware upgrade is supported to improve the sound quality.

All digital mode settings can be done on the panel (without turning on the machine).

The back board of the machine is equipped with a firmware upgrade interface (there is no need to open the machine to upgrade the firmware).

Accusilicon clocks used by motherboard:

R-1 (2021) features:

1. USB not only transmits IIS signal to FPGA processor, but also receives synchronous clock signal sent by FPGA processor. USB interface is no longer equipped with data clock. Synchronous clock is used to make signal transmission more accurate, and the sound quality is greatly improved to the sound quality of the previous generation R-1 plus di-20 (but not di-20he)( New upgrade)

3. FPGA data processing mode is parallel processing mode.

IIS signal is a serial data mode, each data needs a clock cycle, a frame or so channel data needs 64 clock cycles, which is affected by the stability of 64 clock cycles.

The parallel mode only needs one clock to transmit and process the 32-bit data of left and right channels, which greatly improves the processing speed and is not affected by the clock stability.

The input data of IIS (USB and hdmi-iis) is immediately reconstituted into two groups of 32-bit parallel data. The SPDIF signal is demodulated and sent to the next stage for processing by two groups of 24 bit parallel data. DSD data is also a re input on the composition of two groups of 64 bit parallel data processing.

Compared with listening, parallel processing mode can make the sound clearer, neutral, dynamic and more analog.

4. The clock management design of the new architecture makes the clock work more stable, more transparent and more detailed.

5. DSD uses the built-in asynchronous clock to re calibrate, which significantly improves the clarity and dynamic of the playback.

6. SPDIF supports DOP playback.

Advantages and disadvantages of R-2R DAC:

Advantage:

1, R-2R does not convert the clock signal to the output signal.

2. R-2R is not sensitive to jitter, but delta sigma is quite sensitive.

3. The accuracy of output signal level of R-2R is higher than that of delta sigma

Disadvantages:

1. The harmonic distortion of R2R can be quite low, but it can not be as low as es9038 pro (delta sigma).

2. The accuracy of glitch and step resistance is not easy to solve.

Popular R-2R design on the market:

Whether it&x27;s DIY kits or factory products, R-2R has become popular.

In the low price DIY Kit market, the usual design is to learn the old technology of MSB, but only retain the part of signal conversion and abandon the original factory&x27;s exquisite design. This design converts data to analog signal through serial input to shift register IC, which can&x27;t solve the technical problem of R-2R at all. The performance of this design completely depends on the precision of step resistor.

The factory products in hi end market use quite complex technology to solve the problems of R-2R, so as to achieve high performance and sound quality. Some manufacturers use serial control mode of shift register IC.

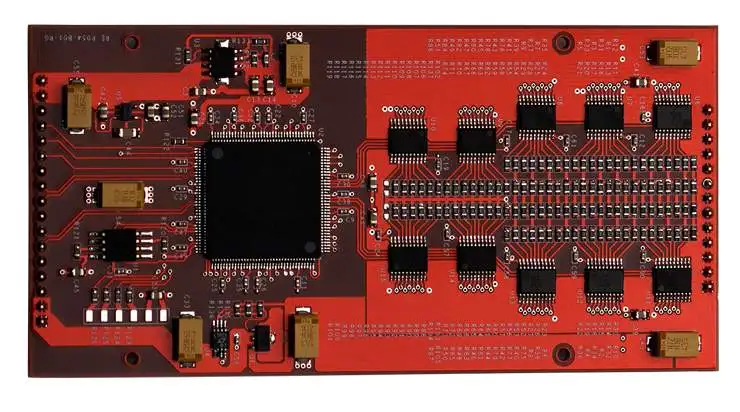

The design in the figure below uses FPGA to control the ladder resistance switch in parallel. In parallel control mode, each bit ladder resistance switch is controlled separately, so it has ultra-high speed (parallel mode only needs one clock cycle to output all data, and serial mode needs at least 8 to 24 clock cycles) to send or update data, and can correct data at any time, so that the output signal has low distortion characteristics, Solve the problems caused by resistance tolerance and glitch.

Accuracy of step resistance:

Many people only care about the accuracy of the step resistor. They think that R-2R depends on the accuracy of the resistor.

Nowadays, 24 bit is a standard, but can the precision of resistance be made to 24 bit?

Even if it is 16 bit, the accuracy requirement is 1 / 66536. Even if the resistance accuracy is 0.1% (1 / 1000), it is not enough. Even if it is 0.01% (1 / 10000), it still can not meet the requirement of 16 bit, let alone 24 bit

Therefore, the accuracy of resistance is not the direction to solve the problem. If there is 0.00001% resistor in the world, it can meet the requirement of 24 bit, but the discrete internal resistance of the step resistor will completely erase the advantage of super high accuracy.

We need to solve the problem technically, not just by improving the accuracy of the resistor. But we still use ultra-high precision resistors in our products.

Very important FPGAs:

FPGA is a programmable logic array device.

Nowadays, FPGA has been used in many hi end DAC products, such as the popular rockna wavedream DAC

The internal hardware layout of FPGA can be designed and arranged by complex software, and the hardware can be upgraded by software upgrade.

When the firmware is upgraded, the hardware is upgraded at the same time. This kind of design has high flexibility. It can improve the sound quality through software upgrade, add more updated functions, and make the product never lag behind the times.

FPGA / CPLD is very important

FPGA / CPLD is a programmable logic array device.

Nowadays, FPGA has been used in many hi end DAC products, such as the popular rockna wavedream DAC

Since 2008, we began to use FPGA design in DAC products.

The digital circuit is composed of one FPGA and five CPLD chips.

The internal hardware layout of FPGA can be designed and arranged by software, and the hardware can be upgraded by software update.

When the firmware is upgraded, the hardware is upgraded at the same time. This kind of design has high flexibility. It can improve the sound quality through software upgrade, add more updated functions, and make the product never lag behind the times.

Responsible FPGA / CPLD

1. High performance SPDIF demodulator is built in FPGA instead of low performance SPDIF demodulator chips such as DIR9001, wm8805 and ak411x

2. Reorganize clock and FIFO technology, output data can be accurately synchronized to clock, reject jitter

3. Built in 2x, 4x and 8x digital filters, and different algorithms NOS mode, for users to choose the most personal voice.

4. Simulate the timbre of tda1541 + saa7220 through unique design.

Powerful power supply design:

13 groups of ultra-high speed and ultra-low noise power supply are built in the DAC, and a dual voltage regulator is formed to better eliminate the power noise and supply power to different parts.

Please be noted:

Even if the product is delivered after 100 hours of aging, according to the feedback of many users in the past, it needs at least 300 additional hours of aging to reach a better state. When aging, it is best to connect the signal source to play music( Turn off the amplifier if you don&x27;t want to listen to music)

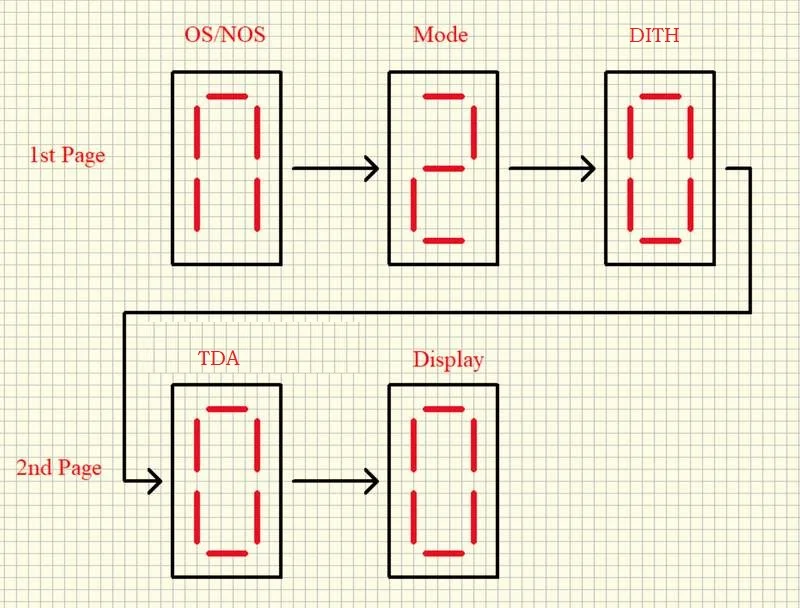

Function introduction:

The DAC can set internal processing functions from the panel to change the voice style without opening the chassis.

Important note:

When you are ready to press the "setting" button, we suggest that you turn down the volume of the amplifier and stop the music playing of the signal source.

Due to the best sound quality, the DAC does not have a mute function. When the internal setting is changed, the DAC will output line switching sound.

When no more buttons are pressed for about 5 seconds, the display will no longer flash. The user can click to play the music of the signal source and turn the amplifier volume back to the normal listening volume.

Setting button:

According to the setting menu, it is divided into two pages. The first page has three digit LED display and the second page has two digit LED display.

Press once, a display bit in the display screen will flash, indicating that this bit function can be changed. Press the "selector" button to change its setting function. When the display flashes, press the "setting" button again, the next display bit will flash and the setting can be changed. If you press the "setting" button again while synchronizer is flashing, the menu will go to the second page.

OS / NOS (oversampling supersampling Technology)

"O" is to select supersampling Technology (OS), "n" is to select no supersampling Technology (NOS).

Mode ( OS and NOS modes):

When OS / NOS is set to "O", the DAC works in supersampling mode, and the lower digital OS mode makes the sound thick, warm and soft. Or depending on your preference for sound.

Mode "0": NOS mode of traditional technology

Mode "2" : 2X oversampling.

Mode "4" : 4X oversampling .

Mode "8" : 8X oversampling.

When the OS is set to "n", the DAC works in NOS mode, and the new architecture configuration is upgraded in NOS mode, so the display shows 1-3, and the result is that there is only one NOS mode.

DITH :

Activate (1) PLL or disable (0) for all inputs.

TDA: (simulation saa7220 + tda1541a)

Activate (1) DAC will simulate saa7220 + tda1541a function operation. The attenuation of digital filter is reduced from - 130dB to - 55dB. We suggest that when this function is enabled, set the OS to OS2 or OS4. Saa7220 runs at 4 times the super sampling rate. However, this function can affect the timbre in any mode.

Display function:

Activate (1) the automatic closing function of the display screen, and the display screen will automatically close after stopping operation for about 10 seconds. Disable the (0) screen auto close function, and the screen will be on all the time.

Selector button:

When the display does not flash, it can be used to select the input signal source.

When the display is flashing, it can be used to change the function settings.

HDMI definitions: (compatible with PS audio format),

The MLCK signal is not required for this unit, but it will not be affected even if the signal source has MLCK output.

Firmware upgrade guide:

There is an upgrade interface on the rear panel of the product, users can connect to upgrade the FPGA firmware and Amanero firmware without opening the machine to upgrade.

UPDATE PORT 10-pin socket.

Connect the Altera Blaster downloader to upgrade the internal FPGA firmware through the computer to upgrade the functionality or performance.

UPDATE PORT toggle switch.

Used to upgrade the built-in Amanero firmware.

Parameter test is the state of the product set to OS8 and after the calibration of the sound, we continue to pursue the sound more like the real, more musical and analog flavor, such as the parameters have changed will not be informed.